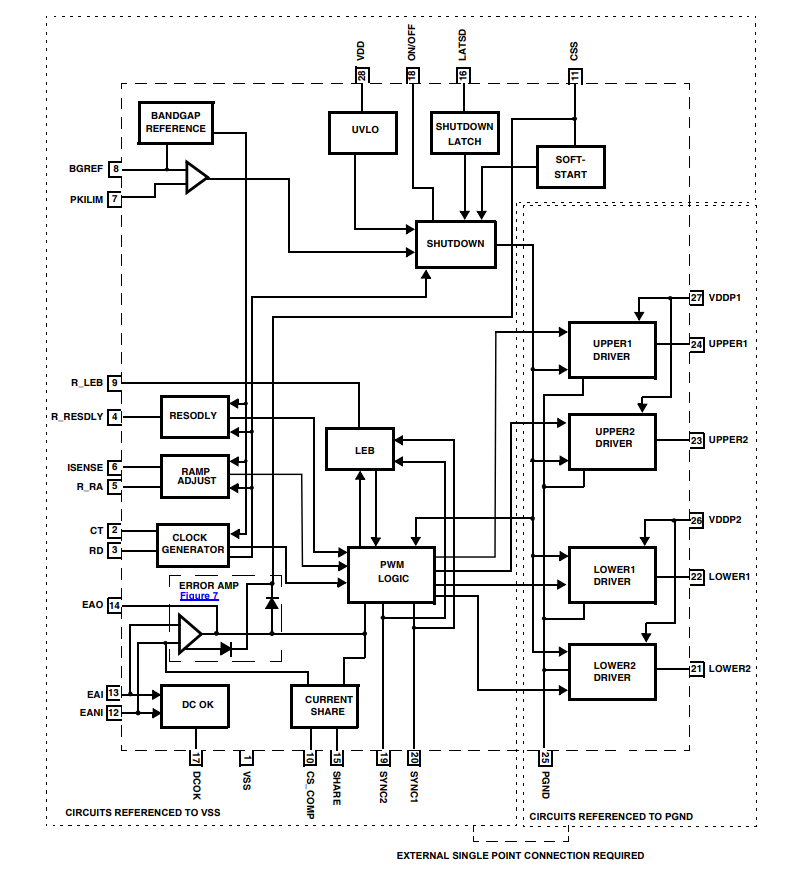

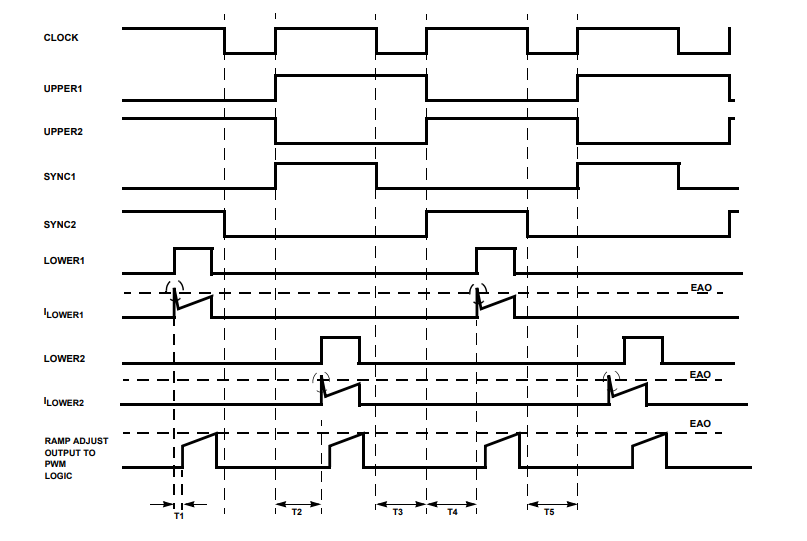

The ISL6551 is a zero-voltage switching (ZVS) full-bridge PWM controller designed for isolated power systems. This part implements a unique fixed frequency zero voltage current mode control algorithm to achieve high efficiency and low electromagnetic interference. The two lower drivers are controlled by trailing edge PWM and use resonant delay, while the two upper drivers drive at a fixed 50% duty cycle.

Pin Configuration

The IC integrates many of the features of the 28-LD SOIC package to produce a complete and complex power solution. Control features include programmable soft start control start, programmable resonant delay zero voltage switch, programmable front blank to prevent error triggering of PWM comparator due to front peak current ramp, ramp compensation adjustable ramp, drive signal to achieve synchronous rectification in high output current, ultra-high efficiency applications and current sharing support for up to 10 units in parallel.

This helps achieve higher reliability and availability as well as better heat management. Protection features include adjustable period peak limiting current protection, fast short circuit protection (in short circuit mode), latching off input to completely turn off IC in case of output overvoltage conditions or other extreme and undesirable failures, non-latching enable input to receive enable commands while monitoring the converter's input voltage and thermal conditions, and VDD undervoltage locking and hysteretic.

Functional Block Diagram

In addition, ISL6551 includes high-current high-side and low-side signpole drivers to avoid additional external drivers for medium-gate capacitor (up to 1.6nF at 1MHz) applications, uncommitted high-bandwidth (10MHz) error amplifiers for feedback loop compensation, and uncommitted high-bandwidth (10mhz) error amplifiers for feedback loop compensation. Accurate band gap reference with ±1.5% (ISL6551AB) or ±1% (ISL6551IB) tolerance under recommended operating conditions, and "in tune" monitor with ±5%.

Drive signal timing diagram

Shutdown sequence diagram